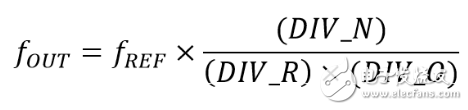

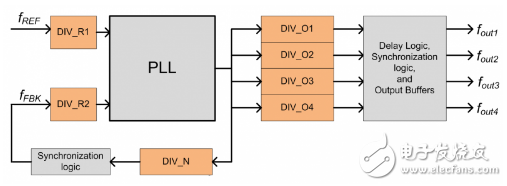

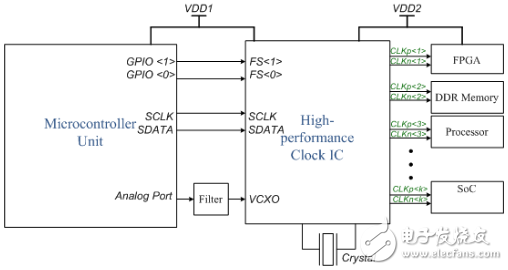

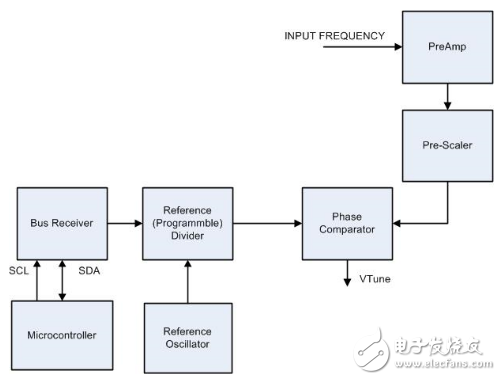

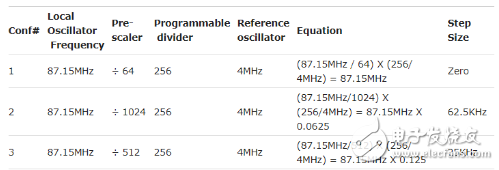

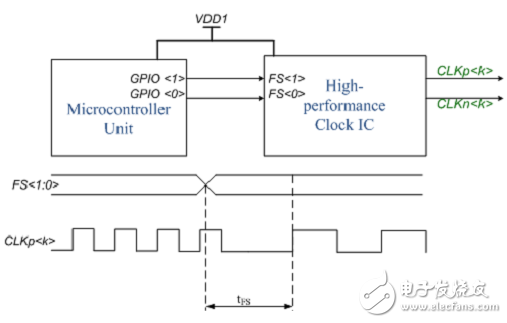

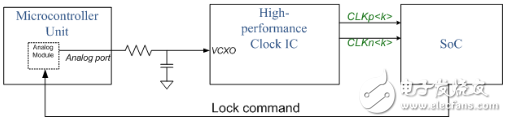

The clock device design uses an I2C programmable fractional phase-locked loop (PLL) to meet high-performance timing requirements, which produces a frequency of zero PPM (parts per million) of synthesis error. High-performance clock ICs have multiple clock outputs that drive subsystems of applications such as printers, scanners, and routers, such as processors, FPGAs, data converters, and more. Such complex systems require dynamic updates of the frequency of the reference clock to implement many other protocols such as PCIe and Ethernet. The clock IC is an I2C slave and requires the host controller to configure the internal PLL logic whose control logic can be written to the microcontroller. As an I2C master, the microcontroller will configure the internal volatile memory written to the clock IC and control the PLL. Therefore, the dynamic update of the system clock frequency can be performed by the on-board MCU-IC combination. Programmable microcontrollers provide control logic for high-performance clock ICs, making overall design more compact and reducing final material costs by reducing on-board ICs and on-board traces. Theory of operation Figure 1 shows the basic PLL architecture for a high-performance clock device. This design uses a scaling factor to provide clock synthesis for the PLL output port. The basic formula for the final output frequency is: fREF is the input reference crystal frequency (typically 8 MHz to 48 MHz in most applications). DIV_R (DIV_R1 and DIV_R2) is the division factor of the input frequency reference. This type of divider is called a prescaler. DIV_N is the fractional-N factor. DIV_O (DIV-O1, DIV-O2, DIV-O3, and DIV-O4) is the post-divide factor before output. Figure 1 PLL architecture block diagram of a simplified high-performance clock The orange block diagram in Figure 1 is a parameter, and the equations using these parameters are programmable equations. These parameters can be written to the non-volatile memory of the clock device at the factory. The clock device has internal volatile and non-volatile memory, and the two memories copy their contents to each other. The non-volatile memory is already written to the desired configuration at the factory. In the final application, the contents of the non-volatile memory are copied to the volatile memory when the device is powered up. At the same time, the PLL produces the required default clock output. One of the important features of the clock IC is runtime programming through the I2C interface. Programmable features allow the user to change the volatile memory contents of the device for immediate changes. The instant programming of the user profile can be implemented through the host controller using the appropriate I2C instructions. The device's non-volatile memory can also store predefined multi-user configurations. The user can use the Frequency Select (FS) function to select one of the configurations. The FS-bit is the CMOS input pin available in the device. The FS pin uses an N-bit external CMOS signal and then internally selects a configuration file stored in non-volatile memory. This configuration file is also copied to volatile memory, and the PLL outputs a different signal. At the same time, the microcontroller provides data through I2C to control the high frequency clock. The advantage of using a microcontroller is that it has different communication peripherals and communication protocols, such as I2C, SPI, UART, Bluetooth, ZigBee, etc., enabling the system to transfer data to other microcontrollers in a master-slave configuration, or to use A custom app is transferred to Android and iOS devices. In addition, the microcontroller comes with a variety of IDE tools to simplify the design. This is a good proof that it is appropriate to use I2C instructions to configure PLL parameters and to write and validate custom applications. High-performance clock application requirements High performance clock ICs are designed for consumer, industrial and networking applications. These clock ICs feature multiple differential and single-ended outputs derived from different PLLs and are programmable through the I2C interface. In addition, high-performance clock ICs support reference clocks for critical interface standards such as PCI Express (PCIe) 1.0 / 2.0 / 3.0, USB 2.0 / 3.0, and 10 Gigabit Ethernet (GbE). Other value-added features such as voltage controlled crystal oscillator (VCXO) and frequency selection (FS) are also supported. The high-performance clock IC is designed to implement the I2C slave mode. Therefore, an onboard I2C host is required to control the following programmable features: · In-system programming via the I2C interface · Update configuration via frequency selection (FS) pin · External reset operation · Voltage controlled crystal oscillator (VCXO) operation Figure 2: Microcontroller - High Performance Clock Interface Circuit The role of microcontrollers in clock IC PLL control Connect the clock IC to the microcontroller circuit as shown in Figure 2. The clock IC has an internal PLL block whose function is to provide a tuning voltage (Vtune) as a fixed DC voltage, and the tuning voltage will vary with the frequency band. The PLL module receives the local oscillator frequency at the input and amplifies the signal by an internal preamplifier. In addition, the prescaler downconverts the input frequency and passes it as an input to the phase comparator. Figure 3: Microcontroller control for the PLL module. The microcontroller sends data to the programmable divider through I2C. The divider also receives input from a reference oscillator such as a 4 MHz crystal oscillator. The phase comparator (ie, phase detector) receives the local oscillator frequency (eg, 87.15 MHz) through the prescaler and also receives the input to the microcontroller (eg, 87.15 MHz) by reference to the divider and reference oscillator. If both inputs match, the phase comparator will provide the Vtune tuning voltage. Once there is a slight mismatch between the local oscillator frequency and the microcontroller frequency data, the tuning voltage (Vtune) and output will not be available. Figure 3 shows the complete block diagram. With the help of a microcontroller, the PLL generates a closed loop by tuning the local oscillator frequency and produces a tuning voltage at the output. The tuning voltage will increase from the lower frequency channel to the higher frequency channel. The microcontroller can adjust the step size by changing the values ​​of the prescaler and the programmable divider. Step size = (local oscillator frequency / prescaler) X (programmable frequency divider / reference oscillator) Table 1 shows some configurations In-system programming via the I2C interface In-system programming enables fast and efficient iterations of system design. The programming data sequence can be transferred to the clock device via the SCL and SDA pins, and the sequence of operations is programmed into the onboard microcontroller (master) to interact with the slave clock at run time via commands and data. Here is an example of the system where the clock signal must be in multiples of the sample rate. This clock frequency varies between the two frequencies of 155.52 MHz and 156.25 MHz. This means that the clock driving the serial controller must be able to switch between these two values ​​flexibly. The microcontroller master can access and modify the PLL configuration written to the volatile memory to meet these two frequency requirements. Update configuration via frequency selection (FS) pin High-performance clock devices support multiple user profiles with personalized configurations. In terms of FS pin conversion, high-performance clock devices have two timing specifications - fast switching and slow switching. Fast switching is available for output ON/OFF, output crossover value changes, and output MUX setting changes. Slow switching is useful for changing PLL parameters (including PLL ON/OFF). As the name suggests, the output changes faster in fast switching, while slow switching is slower. Both switch types can turn the output on or off without any errors. Figure 4 shows the timing relationship between FS and the output clock. Figure 4: Frequency selection operation External reset operation: When the external reset is in effect, the clock IC enters the low power mode. The output and I2C bus signals are in a high impedance (HI-Z) state until the external reset is canceled and initialization is complete. The external reset restarts the volatile memory contents, and the configuration stored in the non-volatile memory is copied to the volatile memory. This feature will be used when you need to reinitialize an application running on any system. Voltage Controlled Crystal Oscillator (VCXO) Operation: For some applications, the output clock frequency should track the input data stream by using analog feedback. As shown in Figure 5, the clock IC is part of the large phase-locked loop. The ASIC or SoC is responsible for tracking the input stream, calculating the error and generating a PWM signal (usually), and then feeding back the error information to the local clock generator for frequency tuning. Figure 5 VCXO example circuit The VCXO function can modify the PLL frequency so the frequency pull does not depend on crystal characteristics, temperature, voltage, or device process. VCXO modulation is linear and precise modulation. A clock reference can also be used. With the built-in analog module of the microcontroller, the VCXO's control logic is accurate to 6 decimal places. As an I2C master, the microcontroller will configure the internal volatile memory written to the clock IC and control the PLL. Therefore, dynamic update of the system clock frequency can be achieved through the onboard MCU-IC combination. Developers can use programmable microcontrollers to provide control logic for high-performance clock ICs. This reduces the need for on-board ICs and traces, making the overall system design more compact. The microcontroller is equipped with powerful IDE tools to accelerate application development. Integrated Programmable System-on-Chip (PSoC) devices further simplify design and help reduce overall product cost. For more details on high-performance clock IC designs, see Getting Started with 4-PLL Spread-Time Clock Generators and Design Best Practices for Spread-Time Clock Generators. Soft Starter,Ac Motor Soft Starter,Soft Starter For Machinery,3-Phase Soft Starter Zhejiang Kaimin Electric Co., Ltd. , https://www.ckmineinverter.com