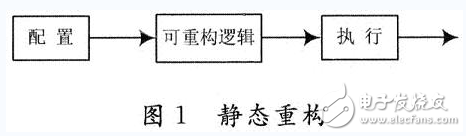

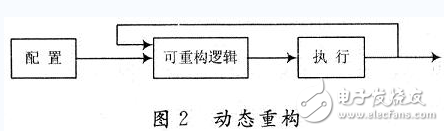

Due to the complexity of the functions of digital logic systems, the chips of monolithic systems are moving toward ultra-large scale and high density. For a large-scale digital system, the system size is based on a combination of various logical function modules. However, whether it is a sequential logic system, a combinatorial logic system, or a combination/timing hybrid system, from the time axis, each functional module in the system is not always working, but is rotated according to the overall requirements of the system. It is activated or working cyclically. Moreover, with the expansion of the scale of digital logic, under the same speed conditions, the average usage rate of its functional modules will decrease in a certain time interval. Therefore, the system design should shift from the traditional pursuit of large-scale, high-density direction to how to improve resource utilization and realize larger-scale logic design with limited resources. Reconfigurable computing technology provides hardware efficiency and software programmability. It combines the features of microprocessors and ASICs and is variable in both spatial and temporal dimensions. Reconfigurable is the dynamic change of the structure of the circuit in the working state of the electronic system. This is done primarily by reconfiguring or partially reconfiguring the programmable logic devices in the system. With reconfigurable technology, the system can have both software implementation and hardware implementation advantages with only a small amount of hardware resources added. According to the way of reconstruction, system reconstruction can be divided into static system reconstruction (StaTIc ReconfiguraTIon) and dynamic system reconstruction (Dynamic ReconfiguraTIon). 1.2.1 Static System Reconfiguration Static system reconfiguration refers to the static overloading of the logic function of the target system, which can only be configured before running, as shown in Figure 1. The FPGA function is re-downloaded by different target system data stored in the memory under the control of external logic, thereby realizing the change of the logic function of the chip. 1.2.2 Dynamic System Reconfiguration Dynamic system reconfiguration refers to a reconfigurable system that can be configured in real time during operation, as shown in Figure 2. For digital logic systems with time series changes, the timing logic is not generated by calling different regions and different logical resources in the chip, but by dynamic dynamics of local or global chip logic for FPGAs with dedicated cache logic resources. Constructed quickly. The FPGA of the dynamic system structure has Cache Logic. Under the control of external logic, the chip logic is globally or locally modified quickly by the cache logic, and the dynamic configuration of the system is accelerated by the resource configuration with control relocation and routing. Structure. In terms of the area of ​​dynamic reconstruction, it can be divided into global reconstruction and local reconstruction. (1) Global reconstruction. It can and can only be completely reconfigured for an FPGA device or system. During the configuration process, the intermediate results of the calculation must be taken out and stored in an additional storage area until the new configuration function is completely downloaded. The circuits before and after reconstruction are independent of each other and are not associated. (2) Local reconstruction. Partial reconfiguration of the reconstructed device or system, while the rest of the local operating state is unaffected. Local reconstruction has a considerable advantage in reducing the range of reconstruction and the number of elements, greatly reducing the reconstruction time. In the past, FPGAs that were commonly used for dynamic reconfiguration research include Xilinx's XC6200 series and Atmel's AT6000 series. They are also based on the SRAM structure, but the individual units of the SRAM are able to access the configuration separately, ie local reconstruction. Their functions do not affect each other and thus have the characteristics of local reconstruction. The advantages of doing so are significant, but they also pay for the increase in hardware circuit size and power consumption. Ultimately, to achieve full real-time reconstruction of the electronic system, FPGA devices with dynamic local reconstruction should be used, such as Xilinx's Virtex-4 series. The feature of FPGA local dynamic reconfigurable technology is to decompose the whole into different combinations according to function or timing, and perform local dynamic reconstruction on the chip according to actual needs, and realize large timing system with less hardware resources. Overall function. Figure 3 shows a typical FPGA local dynamic reconfigurable. It can be seen from FIG. 3 that under the control of the external logic, the local reconstruction of the chip logic can be dynamically performed in real time. Dynamic restructuring of the system is achieved by controlling the resources of the layout and wiring. In order for the FPGA to effectively implement real-time system dynamic reconstruction, the FPGA must meet the following requirements in terms of structure: (1) Not only has reprogrammability, but also dynamically reconfigures system resources without disrupting global or local logic operation capabilities in the device. Many traditional FPGAs store configuration data in an external serial EPROM. There are three disadvantages to this approach: the entire FPGA must be stopped before refactoring; only the entire FPGA is reconstructed; the previous internal state of the FPGA cannot be saved during refactoring. The new dynamic reconfigurable FPGA does not need to trigger the reset signal before reconstruction, but turns off the clock of a part of the logic circuit in the FPGA chip, then reconfigures the logic circuit and finally recovers the clock signal. (2) The internal configuration information of the FPGA is symmetrical. At any time, any general basic logic function can be configured at any position of the device, and a simple model combination is used to realize the complex functions in the juice setting. Air Circulation Fryer,Electric Oil Less Fryer,Large Capacity Air Fryer,Multi Function Air Fryer Oven Ningbo ATAP Electric Appliance Co.,Ltd , https://www.atap-airfryer.com