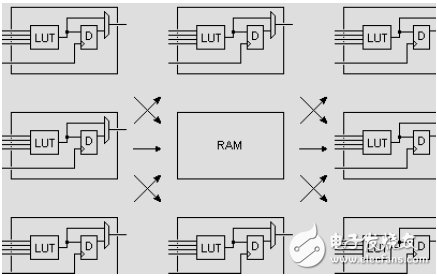

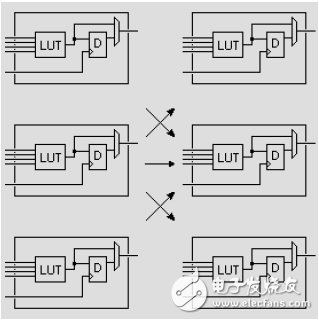

Digital clock management is available in most FPGAs in the industry (all of Xilinx's FPGAs have this feature). Xilinx offers state-of-the-art FPGAs that provide digital clock management and phase loop locking. Phase loop locking provides accurate clock synthesis and reduces jitter and filtering. Most FPGAs have embedded block RAM, which greatly expands the range and flexibility of FPGA applications. The block RAM can be configured as a common storage structure such as single port RAM, dual port RAM, content address memory (CAM), and FIFO. RAM and FIFO are relatively popular concepts and will not be redundant here. The CAM memory has a compare logic in each of its internal memory locations. The data written to the CAM is compared to each of the internal data and returns the address of all data identical to the port data, thus the address at the route. There are a wide range of applications in the switch. In addition to block RAM, the LUTs in the FPGA can be flexibly configured into structures such as RAM, ROM, and FIFO. In practical applications, the amount of internal block RAM in the chip is also an important factor in selecting a chip. The single-chip block RAM has a capacity of 18k bits, that is, a bit width of 18 bits and a depth of 1024. The bit width and depth can be changed as needed, but two principles must be met: first, the modified capacity (bit width and depth) cannot be greater than 18k bits; secondly, the maximum bit width cannot exceed 36 bits. Of course, multiple blocks of RAM can be cascaded to form a larger RAM, which is limited only by the amount of block RAM in the chip, and is no longer bound by the above two principles. The routing resources connect all the cells inside the FPGA, and the length and process of the wires determine the driving capability and transmission speed of the signals on the wires. The FPGA chip has a wealth of routing resources inside, and is divided into four different categories according to the process, length, width and distribution. The first type is the global routing resource, which is used for the internal global clock of the chip and the global reset/set wiring; the second type is the long-line resource, which is used to complete the wiring of the high-speed signal between the chip Bank and the second global clock signal; Classes are short-term resources used to complete the logical interconnection and routing between basic logic cells; the fourth class is distributed routing resources for control signals such as proprietary clocks, resets, and so on. In practice, the designer does not need to directly select the routing resources, and the layout router can automatically select the routing resources to connect the various module units according to the topology and constraints of the input logical network table. In essence, there is a close and direct relationship between the use of routing resources and the results of the design.

B85 8-card mainboard, 8-card in-line motherboard platform (B85 8-card 1820U independent U+ new chassis 4 strong 5300 RPM fan /4 silent 3000 RPM optional +4G memory +128G solid state +2000W new power supply) compatible with all types of graphics cards in the market, stable performance, reasonable heat dissipation.

X79 Gpu Mining Case

Chassis weight: 4.5kg

B85 Gpu Case,B75 gpu case,gpu mining case,gpu case,GPU Server Case Shenzhen YLHM Technology Co., Ltd. , https://www.apgelectrical.com

Weight of chassis with fan: 5.5kg

Size:500*400*180mm

Multi graphics card case custom case

Motherboard bit: compatible with standard ATX motherboard

Hard disk bit: a 3.5-inch hard disk or a 2.5-inch hard disk

Power bit: ATX power installation size

Standard fan: 4 sets of 12038 fans,

Graphics card bit: supports up to 5 330mm long graphics cards

Chassis material: 1.0 mm cold plate full baking paint to prevent rust, anti-static effect!

tips: chassis products are bulky, heavy weight, and the express freight is very expensive. Buyers should consider buying them carefully to avoid unnecessary loss caused by return. If you don't understand, please communicate with customer service.

The fan of the product is double ball fan, 5300 RPM new violent fan, with noise of 65dB

3. Digital Clock Management Module (DCM)

Figure 2-7 Embedded block RAM

Figure 2-8 FPGA internal interconnect wiring