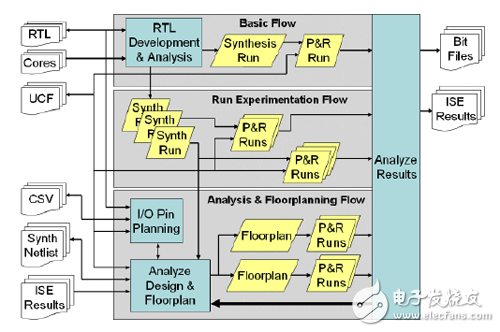

The PlanAhead tool is an integrated, visual FPGA design tool from Xilinx that can be applied to different stages of the FPGA design process. Common applications include RTL source code development with PlanAhead, I/O pin planning, RTL Netlist analysis, layout and routing analysis, layout planning, and Chipscope cores can also be inserted into design-assisted debugging in PlanAhead to improve performance. You can also use PlanAhead to try out different implementations of various implementation properties, applying different timing constraints, physical constraints, and layout planning techniques to improve design performance. We can also import ISE layout results into PlanAhead for analysis, locate critical paths, find the real cause of design performance, and improve design performance by adding reasonable constraints and trying multiple layout planning strategies. PlanAhead has the following features. I/O pin planning. RTL development and analysis. Synthesis and implementation. Design analysis. Static timing estimation. Timing constraint editor. Strong layout planning. Block-based logic design. It is worth mentioning that PlanAhead has been integrated into ISE 11.x, including integrated pre-pin planning - I/O pin planning (Pre-Synthesis), integrated pin planning - I / O pin planning (Post- Synthesis), integrated area/pin/logic planning—Floorplan Area/IO/Logic (Post-Synthesis) and post-implementation timing analysis/design planning—Analyze TIming/Floorplan Design (Post-ImplementaTIon), which replaces the previous Commonly used PACE and Floorplanner tools. As shown in Figure 10-1, the PlanAhead design process consists of three parts: the basic design process, the experimental process, and the design analysis/layout planning process. The following is a brief introduction. Base Flow: This process allows designers to import RTL source files and then synthesize, implement, and analyze results. If you want to conduct design analysis and layout planning, you need to use the design analysis and layout planning process. Run ExperimentaTIon Flow: Designers can apply different design strategies and experiment with multiple synthesis or implementation processes using a combination of multiple synthesis and implementation attributes. The PlanAhead tool provides a number of different implementation strategies, which also allows designers to customize the strategy. For example, a designer can specify area optimization, speed optimization, or power optimization strategies in a comprehensive phase, run multiple integrated processes, generate comprehensive results under different integrated strategies, and then analyze them. Designers can also generate multiple implementation results by setting different translation, mapping, and placement and routing properties during the implementation phase. Analysis & Floorplanning Flow: PlanAhead can analyze the integrated netlist, layout the logical resources and pins, and import the implementation results of ISE into PlanAhead for analysis and layout planning. Figure 10-1 PlanAhead design flow The various design flows are described in detail below. PlanAhead input file: RTL Source File: Source files, including Verilog/VHDL. Xilinx Cores (NGC / NGO): Xilinx nuclear netlist file. XST Constraint Files (XCF): XST constraint file. I/O Port Lists (CSV): I/O pin list file, CSV format. I/O Port Lists (HDL - Verilog or VHDL): I/O pin list file, HDL format. Top-Level Netlists (EDIF): Top-level netlist, EDIF format. Module-Level Netlists (EDIF): Module netlist, EDIF format. Top-Level Netlists (NGC): Top-level netlist, NGC format. Constraint Files (UCF / NCF): Constraint files, UCF/NCF format. Xilinx ISE Placement Results (NCD/XDL): Xilinx ISE layout results, NCD/XDL format. Xilinx TRCE TIming Results (TWX/TWR): Timing Analysis Report. PlanAhead output report: I/O Pin Assignment (CSV): I/O pin constraint file, CSV format. I/O Pin Assignment (RTL - Verilog or VHDL): I/O pin constraint file, HDL format. Log File (planAhead.log): The PlanAhead log file contains the information generated by running the PlanAhead command. You can run Window→View Log File to open this file. Journal File (planAhead.jou): Tcl command file. Error Log Files (planAhead_pidxxxx.debug & hs_err_pidxxxx.log): Error log file. DRC Results (results_x_drc.txt): DRC text file. TimeAhead Results (Excel file): Timing planning file. Netlist Module, Pblock, and Clock Region Statistics Reports: netlist module, physical block, clock domain statistics report. SSN Analysis Report: SSN Analysis Report. WASSO Analysis Reports: WASSO Analysis Report. PlanAhead environment settings information: View Display Options File (planAhead.ini & Window Layout Files (.layout): The window layout configuration file for PlanAhead. Shortcut Schema (default.xml): The shortcut key definition file for PlanAhead. Strategy Files (.psg): PlanAhead implements a policy configuration file. PlanAhead project data file: Project Directory ( Project File ( Project Data Directory ( Relay Control Voltage Regulator

PC-TM series Relay Control Voltage Stabilizer has the low energy consumption,the over voltage protection,the low voltage protection,the over-current protection,the over-loading protection,the over-temperature protection and so on.It boasts for many kinds of protections,the collection energy conservation and the environmental protection ect.This is a brand-new concept product which possess many new technologies!This series products simultaneously ha applied for many technical monopolies

We already applied many kinds of this products patent, and the technical patent NO: 200720036394.1 and Appearance paten NO: 200730025909.3

2. Use for equipment:

Computer

Test equipment

Light system

Safe alarm system

Ray equipment

Medical equipment

Copy machine

Stereo equipment

Numerical control machine tools

Industrial automation equipment

Color and drying equipment

Test equipment

Hi-Fi equipment

Relay Control Voltage Regulator ,Voltage Regulator For Ac,3000Va Voltage Regulator,Wall Mount Voltage Stabilzier zhejiang ttn electric co.,ltd , https://www.ttnpower.com

.patheme): Display the PlanAhead initialization file, and the display properties of the PlanAhead tool are saved in this file.

): Project path, save PlanAhead project files, project data files and ISE implementation results.

.ppr): Project file, save PlanAhead status, project netlist information and various layout planning information are saved in it.

.data): The project data path, which contains all the planning information (Floorplan) in the project and the data related to the netlist.

Chapter 10 PlanAhead Tool Application