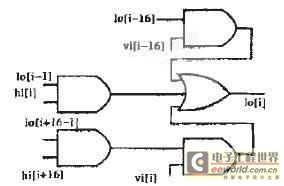

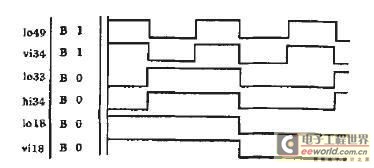

1 Introduction With the rapid increase in chip integration, an electronic system or sub-system can be fully integrated on one chip, and the IC industry has formed a design method based on System-on-Chip (SOC) technology. At the same time, IC design capability and EDA tools are relatively lagging behind the development of semiconductor process technology. The growing gap between the two has become a prominent obstacle in the development of SOC technology. Designing with IP-based multiplexing technology is the only effective way to reduce this gap. IP multiplexing technology includes two aspects: IP core generation and IP core multiplexing. In this paper, IP core multiplexing method and SOC technology are used to design a dedicated PLC microprocessor FSPLCSOC module based on AVR 8-bit microprocessor AT90S1200IP Core. 2 IP core multiplexing IP Core Reuse refers to the design, synthesis, and verification of ERP tools by inheriting, sharing, or purchasing the required intellectual property cores (third-party IP cores) during the design of the integrated circuit. The IP core is the carrier and core content of IP multiplexing. The content of the IP core is also very different based on application requirements, specification protocols and industry standards. In the IC industry, IP cores are defined for use in ASICs, ASSPs, PLDs, etc., and pre-defined functional, validated, reusable circuit functional blocks such as PCI interface cores, ADC cores, FIR filters Core, SDRAM controller core, etc. Depending on the level of IC design. IP cores are classified into the following three categories: Soft IP, Hard IP, and Firm IP. The paper mainly deals with the design and reuse of soft IP cores. Soft IP is an analogous, comprehensive hardware description language (HDL) model, usually a synthesizable RTL model that includes logical descriptions, netlists, and test documentation (Testbench). The soft IP design cycle is short, the investment is small, and it has nothing to do with the process. It can be flexibly modified. Only the timing, area and power consumption need to be corrected in the design, and the reusability is the highest. Soft Core-based design is a very practical SOC design method. It divides the functions of the system into different soft cores, including microprocessor, ALU, ROM, PC, ROM, I/0, and so on. Since the soft IP core only provides a comprehensive HDL description, it is necessary to understand the RTL model described by the HDL file before multiplexing, and use the standard cell library of the appropriate process technology, and then re-integrate, place and route, and post-simulation to extract the netlist. Repeated work such as verifying timing, and finally integrated into the SOC design, so the SOC design generates an integrated IP core and a third-party multiplexed IP core. 3 FSPLC microprocessor IP core design 3.1 IP soft core generation Based on the AVR 8-bit microprocessor, the actual PLC ladder diagram and its instruction list are analyzed. Three modules, such as logic processor LP, Boolean processor BP, and memory bit interface MBI, are used to improve the PLC execution speed. The following is the logical processor LP unit. The module is an example that describes IP soft core generation. PLC ladder diagram includes 8 basic circuits: left branch contact LBC / non-contact LBCN, right branch contact RBC / non-contact RBCN, double branch contact DBC / non-contact DBCN, no branch contact NBC / no branch Non-contact NBCN. According to these 8 basic circuits, a 16xl6 contact matrix circuit, namely the logic processor LP unit, is designed. Each contact in the matrix is ​​simulated by the electronic circuit to simulate the PLC ladder basic circuit. A horizontal line input, a vertical line input, and an output output coil are included on any one of the contacts. There are 256 horizontal line input circle nodes hi in the contact matrix, 240 vertical lines input circle node vi, and 256 output coils Io. When a line exceeds 16, turn to the next line to form a matrix circuit, such as hi[i], vi[i], lo[i] represents the horizontal line input, vertical line input, and output of a contact, then its peer The horizontal input, vertical input and output of the next contact are hi[i+ 1], vi[i+1], lo[i+1], and the next contact in the same column hi[i+16] , vi[i+16], lo[i+16], then the expression of the output contact is I0[i]=I0[i-1]hi[i]+vi[i-16]lo[i-16]+vi[i]lo[i+16-1]hi[ i+16] . In this way, the individual contacts are connected to each other to form a contact matrix for processing the ladder diagram. As shown in Figure 1. Figure 1 LP unit contact electronic circuit simulation The logical processor LP uses Verilog description to perform functional simulation with Model-Sim to verify the correctness of the module function. The LP unit function simulation waveform is shown in Figure 2. Figure 2 LP unit function simulation waveform Once the verification function is correct, the module is synthesized with Synysys' comprehensive tool Synplify Pro. The integration includes Compiling, Mapping, and Optimization. The synthesis will be via ModelSim. The source code of the functional simulation verification is tuned to Synplify Pro, the Compiler is executed, and the constraint file is created after compilation. Sdc, the editing constraint file adds constraints to the module, including clock, area, fan fanout, delay, etc. After the constraint is added, the integration is performed to generate the netlist file. EDF. According to the synthesis given. The log file observes whether the constraints in the Constraint file meet the requirements. For example, according to the given "Worst Path Information, modify the constraints to meet the requirements of the Worst Path. After the completion of the integration, the netlist file is expanded in the Quartus II 4.0, and the layout is compiled and formed. The .sof file, the file is subordinated to the Alters Nios development board for verification, and the verification is performed correctly, and then the model verification is performed by using ModelSim. Our Lithium Battery includes 5G Base Station Backup Power System,like 48V 100Ah/150Ah/200Ah Lithium Battery. 3.2V Prismatic cells,like 3.2V 50Ah/105Ah/202Ah Lithium Battery. And Lithium Ion Pouch Cells, including 3.2V 12-30Ah. Lifepo4 Battery,Lifepo4 Lithium Ion Battery,Lifepo4 48V 100Ah Lithium Ion Battery,Lithium Ion Battery For Solar 100Ah Jiangsu Zhitai New Energy Technology Co.,Ltd , https://www.zhitainewenergy.com